课程介绍

您是对使用 Verilog 硬件描述语言进行数字电路设计感兴趣的初学者还是狂热爱好者?您之前是否尝试过学习 Verilog HDL,但发现它非常具有挑战性?您是否想知道您是否具备成为数字芯片设计师的条件?那么你来对地方了!

Verilog 硬件描述语言像 A、B、C 一样简单

您将学习数字电路理论的基础知识,我们将把大部分精力集中在使用 Verilog 用真实数字电路实现实际编码示例上。您将在 Verilog HDL 中为数字设计和功能验证打下坚实的基础,从而完成本课程的毕业。

从数字设计的角度来看,您将能够:

从数字电路图/原理图开始,为 ASIC/FPGA 实现可综合的 Verilog 代码

从功能描述开始,为 ASIC / FPGA 实现可综合的 Verilog 代码

从功能验证的角度来看,您将能够:

理解数字电路的功能描述并为其创造刺激

实施自检测试平台以验证数字电路的功能

您将轻松区分不同的 Verilog 编码风格(结构、数据流、行为)以及如何使用它们来设计可综合的数字电路。您将看到使用 Verilog 对数字电路建模是多么容易!

在课程结束时,您将掌握 Verilog 行业级编码技术,以获得数字设计或验证的最佳结果。

了解如何使用工业级 Verilog HDL 模拟器

模拟是设计现代数字芯片的关键部分,因此您将安装并学习如何使用 Modelsim – 英特尔 FPGA 版(用于学术目的的免费版本)。您将能够使用世界一流的模拟器创建项目、模拟您的 Verilog 代码并解释输出。

类型:在线学习 | MP4 | 视频:h264,1280×720 | 音频:AAC,48.0 KHz

语言:英语 | 大小:3.36 GB | 持续时间:5h 2m

通过实现组合/时序数字电路和测试平台,构建强大的 Verilog 语言基础

课程大纲

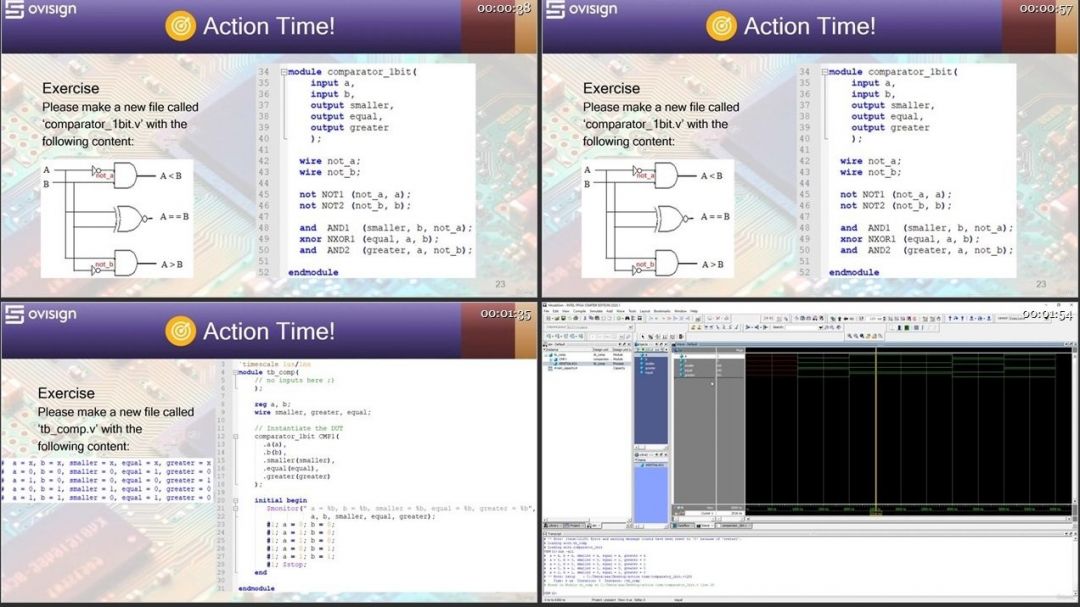

本课程专为对数字微电子、数字电路设计与验证感兴趣的初学者量身定制。该课程包含超过 158 个一口大小的讲座,其中一半以上是标记为 Action Time 的动手练习。每个 Action Time 都有可下载的资源,您可以使用 Modelsim 立即进行模拟。这些部分中的大多数还包含对您的挑战,因此您将编写超出初始功能的额外代码。

您的第一个 Verilog 示例将类似于普通的编程语言(如 C)来学习运算符,并且,我们将逐步推进到硬件描述语言结构,其中 Verilog 过程并行执行。

您将学习如何将 Verilog 用于组合逻辑和时序逻辑,以及如何组合结构 / 数据流 / 行为编码样式以获得具有特定功能的数字电路。随着您的进步,您的电路将变得更加复杂,其中一些由子电路的层次结构组成。

您将在课程中实现的 Verilog 组合电路:逻辑门、加法器、比较器、二进制编码器/解码器、优先级编码器、多路复用器/多路分解器、七段显示解码器、算术逻辑单元 (ALU) 等…

您将在课程中实施的 Verilog 时序电路:触发器、锁存器、移位寄存器(PIPO、PISO、SIPO、SISO)、线性反馈移位寄存器、同步计数器、分频器、序列检测器等…

接下来,您将试验 Verilog 函数和任务,以及如何在测试平台和设计中使用它们。

在最后几章中,您将设计存储器(SRAM 和 ROM)、有限状态机以及更复杂的电路,如 FIFO 甚至数据加密模块。

目标成功的工作流程!

我们从实际工程问题开始,了解数字电路如何解决该问题。

您将看到一个真实的数字电路,它是如何在现实世界中使用的,然后是如何使用 Verilog 对其进行建模和测试。

您使用 Modelsim 对其进行模拟,接下来我将向您介绍结果解释。

我们每次都一起做这个过程……我解释了 Verilog 代码背后的故事,以便在课程结束时,您将能够编写故事背后的 Verilog 代码。

为什么要学习 Verilog HDL?

您周围设备中的所有芯片都是使用 Verilog 设计的可能性超过 50%。

作为数字设计或功能验证工程师工作意味着在今天设计明天的技术。这意味着拥有一份令人兴奋和具有挑战性的工作,对世界产生巨大影响。由于只有不到 2% 的工程师选择了这条道路,而且半导体行业从未如此繁忙,我很确定你会发现自己在其中占有一席之地。

Verilog 是学习 SystemVerilog 的良好基础,SystemVerilog 是半导体行业非常流行的面向对象设计和验证语言。

我为什么创建这门课程?

作为一名工程专业的学生,我发现学习 Verilog 非常具有挑战性,因为它的学习曲线非常陡峭,而且您需要大量的专业知识才能运行一个简单的示例。因此,大多数学生放弃学习 Verilog,转而从事数字设计或验证工作,这也会对他们的学业成绩产生负面影响。

经过 10 多年的行业经验、数千小时的 Verilog 和学术研究,我觉得我找到了过去没有的丢失的拼图。本课程将向您展示使用 Verilog 进行数字电路设计的美感和简单性!

准备好?设置…开始!

感谢您对用于数字电路设计和功能验证的 Verilog HDL 感兴趣!

准备好开始掌握用于数字设计和验证的 Verilog HDL 基础知识了吗?让我们开始这场奇妙的冒险吧!

本课程适用于

计算机科学、电子学、电信和微电子学学生,希望在他们的项目和教师任务中学习 Verilog

电子和微电子学爱好者,希望学习 Verilog 硬件描述语言

初学者渴望从事数字设计职业工程师或功能验证工程师

数字微电子和数字电路设计初学者对 Verilog 硬件描述语言感到好奇

您将学到什么

掌握 Verilog 语言的基础知识,为 ASIC/FPGA 设计可综合数字电路

区分 Verilog 结构/数据流/行为设计风格以及如何/何时在数字设计和验证中使用它们

使用 Verilog 实现组合和顺序数字电路HDL 从原理图或功能规范

开始 从数字电路的功能规范开始创建和模拟 Verilog 测试

平台 使用工业级模拟器检查数字电路在测试平台中接收激励的行为(免费用于学术目的)

对 80 多个可下载代码示例、电路和测试平台的清晰直观的解释,让您提高记忆力并加快学习速度